PCB布局注意这一点,波峰焊接无风险

发布时间:2023-09-12 15:39

高速先生成员--王辉东

网红芬说,世界上最遥远的距离是我就在你对面,而你对我却视而不见,风清云淡,毫无关联。你走你的阳关道,我过我的独木桥,我们是井水不犯河水,安全。

世界上最近的距离,不是心与心的共颤,而是明明知道不可执汝之手,却每每精心装扮,不停的疯狂试探。莫牵手,小手一牵,惊涛拍岸,天崩地裂。

这是人生是爱情,也适用于SMD和DIP。

是近亦忧,远亦忧。近则怕虚焊,怕连锡,怕灌孔率不达标,远则怕空间不足,怕器件摆放不下,怕结构冲突,怕走线过长,怕SI不达标。

客户小蝶见到网红芬后,一脸崇拜的说;“芬芬你这句话,太有内涵了,我很喜欢,弱弱的问一句,这句话的背后有啥故事呀……”

网红芬一声长叹,这还要从我拍高速先生视频的那一年说起,那天我去了车间,看到了客户的一个案例…….

什么是波峰焊

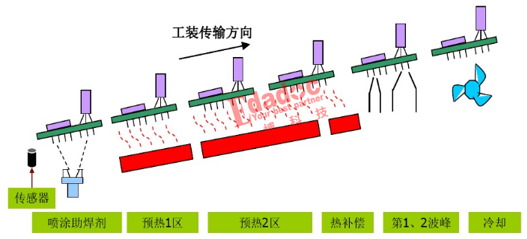

波峰焊是指将熔化的焊料(铅锡合金),经电动泵或电磁泵喷流成设计要求的焊料波峰,使预先装有元器件的印制板通过焊料波峰,实现元器件焊端或引脚与印制板焊盘之间机械与电气连接的焊接设备。波峰焊是让插件板的焊接面直接与高温液态锡接触达到焊接目的,其高温液态锡保持一个斜面,并由特殊装置使液态锡形成一道道类似波浪的现象,所以叫“波峰焊”,其主要材料是焊锡条。

案例描述:

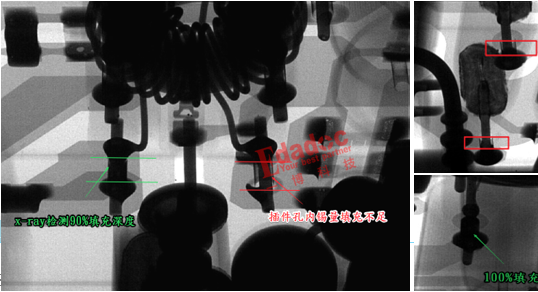

PCB板内的DIP插件,波峰焊后,虚焊,孔内爬锡高度不足,无法满足IPC的二级标准。

IPC二级标准

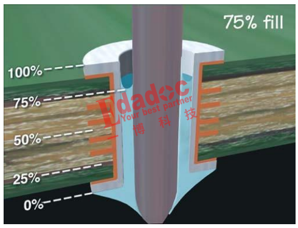

IPC-A-610里面规定,支撑孔焊接的二级标准,焊锡垂直填充最少为75%,允许包括主面和辅面一起最多25%的下陷。

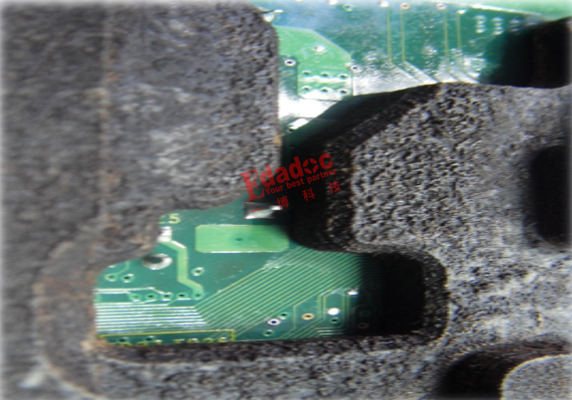

实际用E公司的检测神器X-RAY检测后,效果如下:

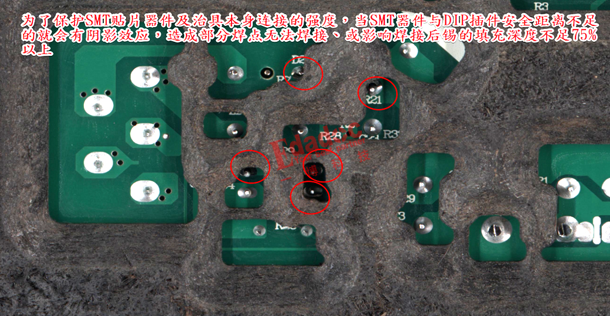

为什么会有空洞不上锡,我们来看这些虚焊的地方,都是插半装器件距SMD器件太近,如下图。

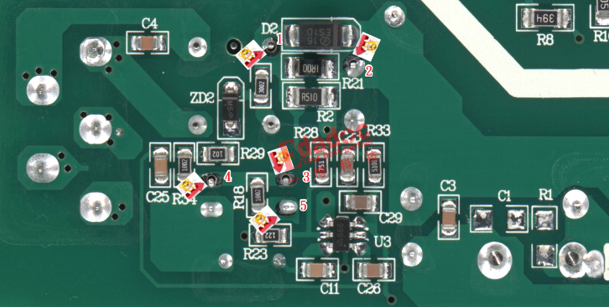

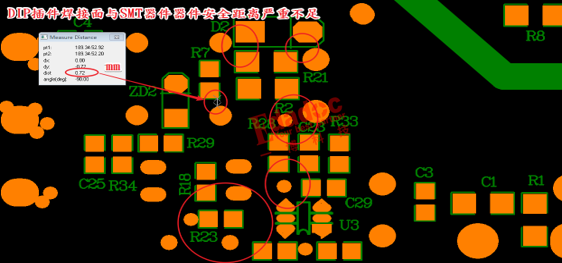

我们再来看,客户的gerber文件,原始设计如下图所示:

安全距离严重不足、多个焊接位置只有0.72mm左右,返修工时多,增加客户成本;

载具开制存在一定的阴影效应,并且器件越高,间距越近,这种阴影效应越明显,品质不良的风险越高。

有人说用烙铁加锡就可以了,真的是这样吗,小蝶问道。

烙铁焊接品质没有波峰焊接的好,爬锡率是个问题,同时还会影响出货周期;

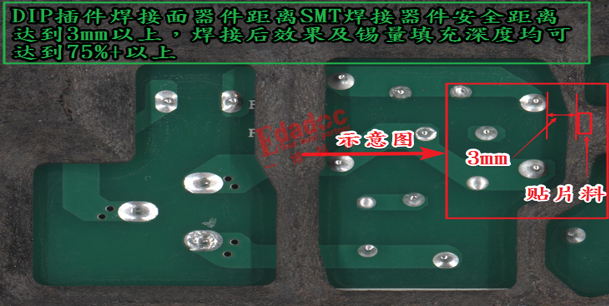

以下是来自SMT工厂的真诚建议:

背面DIP Pin脚与SMD零件距离标准:零件高度≦3mm, 背面DIP Pin 脚与SMD零件距离(x)需≧3mm;

SMD器件越高与DIP插件焊接面安全距离就要越大,至少需≥5mm。

所以品质的建立和设计有密切的关系。