很难相信,这对高速信号换了那么多次过孔!!!

发布时间:2021-10-18 17:12

作者:一博科技高速先生自媒体成员 黄刚

PCB工程师:“没有层走了,这几对10G信号要多换几次层,要打4次过孔才能走过去啊!”

SI工程师:“……”

不知道粉丝里面做PCB设计的朋友们有没有上面所说的困难呢?由于老板或者客户成本要求很高,层数只有那么几层,高速信号还特别多,而且多就算了,还特别不顺,有交叉,有交叉就意味着中间可能需要多换几次过孔,但是速率又不低,要求保证很好的信号完整性,当你用颤抖的双手拉好这几对换了4、5次过孔的高速信号后,连自己都觉得信号质量会挂!!!

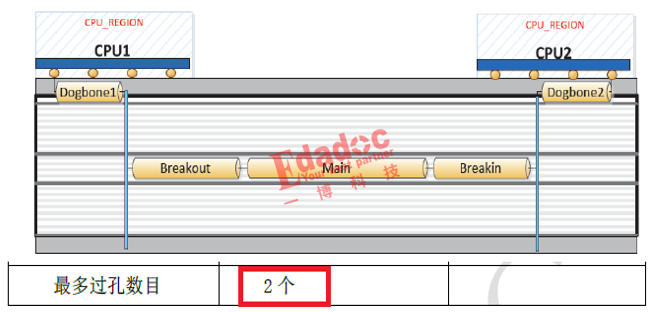

关键是你们公司还没有能做仿真验证的同事,而且你这块板子的设计要求又明确的写着:从发送芯片到接收芯片最多只允许……2个过孔!对,你没看错design guide,是2个!

经过相当“漫长”的设计加工测试后,唰的一声,高速先生就得到了它们的第一手测试结果,本来还想多说几句理论的东西,但是相信粉丝们都迫不及待的想看对比结果了,我们就把理论的东西放在后面来讲好了。

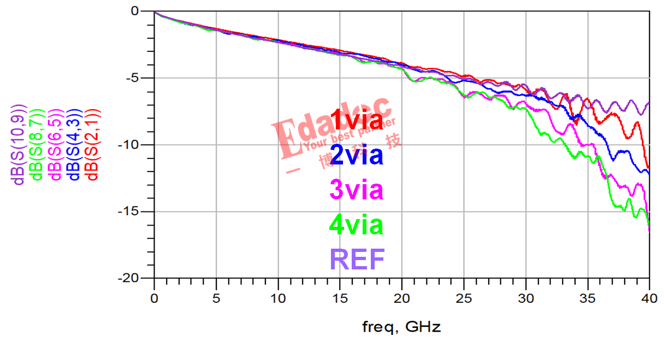

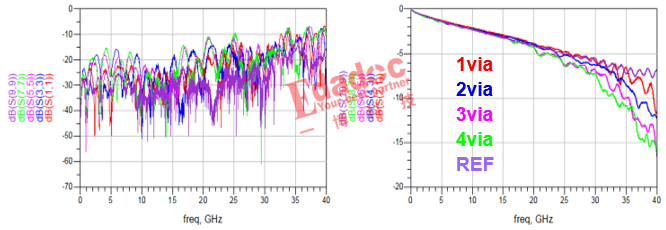

那我们先来一睹这几种case的测试结果,我们测试到了很高频的40GHz,分别来它们的回波损耗和插入损耗,其中从回波损耗看没有太明显的区别,说明从过孔的阻抗优化得很好,增加换层过孔基本不会带来太多阻抗的失配,从而导致回波损耗的变差。但从插入损耗来看就能看出区别了,在20GHz以后增加一个过孔带来的损耗影响会变得明显,尤其在30GHz之后,过孔本身的能量辐射和流失会变得严重,也是意料之中的事情。

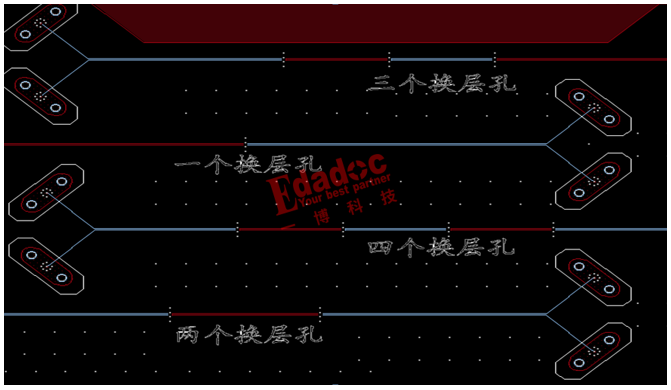

这个待测物包含了从一个过孔到4个过孔的换层走线结构,当然高速先生还做了一根参考线(REF线),也就是没有过孔的单纯走线和他们4种case来对比了。 经过相当“漫长”的设计加工测试后,唰的一声,高速先生就得到了它们的第一手测试结果,本来还想多说几句理论的东西,但是相信粉丝们都迫不及待的想看对比结果了,我们就把理论的东西放在后面来讲好了。

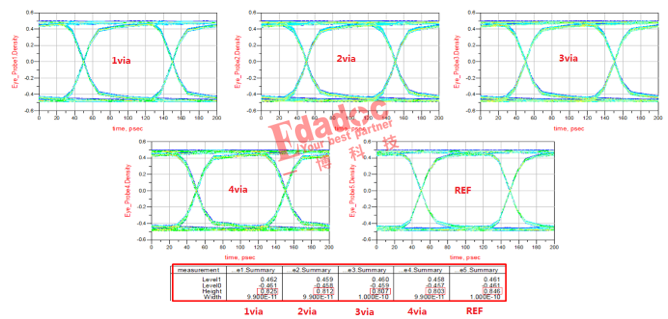

当然可能还有部分粉丝看不懂上面这些频域的损耗曲线,那我们就用时域的方法继续和大家分享这次的测试结果哈。我们分别在以上的过孔换层链路上去传输10G的信号,我们通过时域眼图的方式来看看它们的影响。

于是我们得到了上面5种case的眼图结果,从结果上看到,从REF到4个换层过孔,我们能看到这10G信号眼图的眼高从845mV减小到803mV,但是总体上不会对性能有特别大的影响。

为什么从眼图上看,10G信号的眼图差别不会特别大呢?因为回到我们的插入损耗来看,在10G的位置的确也是差别不大,频域上的差别不大其实就能对应到时域上的差别不大了!

总结一下这篇文章的核心内容哈,高速先生从自己做的测试板来看,对于高速信号经过多次换层过孔的性能是这么看的:多增加一个经过优化的换层过孔,是不会对高速信号的性能有非常大的影响!但是这个前提很重要,那就是“经过优化”的换层过孔!再突出一次,是经过优化的过孔!