我走过太多的路,却走不出DDRX调试的套路

发布时间:2022-04-25 15:20

作者:一博科技高速先生周伟

阳春三月,春暖花开,草长莺飞,处处透着生机和浪漫,也是一年中最美好的时光,可是由于疫情,很多人的生活、工作等节奏和安排也都被打乱了,雪上加霜的是,攻城狮豹哥还遇到了一件尴尬的事情,之前设计的一个项目在研发打样阶段调试一切正常,这次重新生产贴片了几百片小批量的,结果却发现有一些不良,关键是还没有找到解决办法,天天被客户催着找问题,真是一个头两个大。

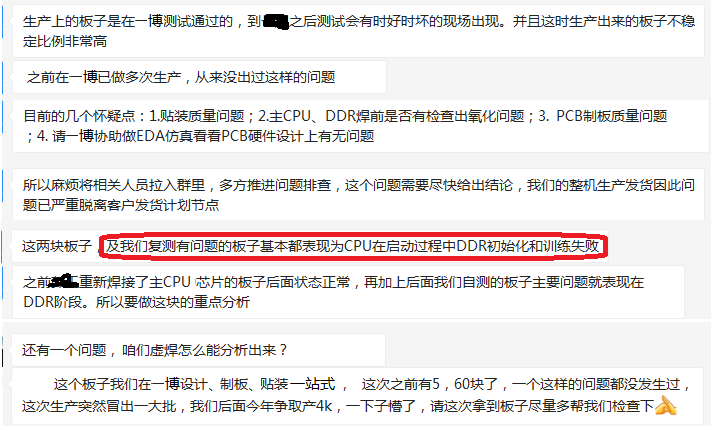

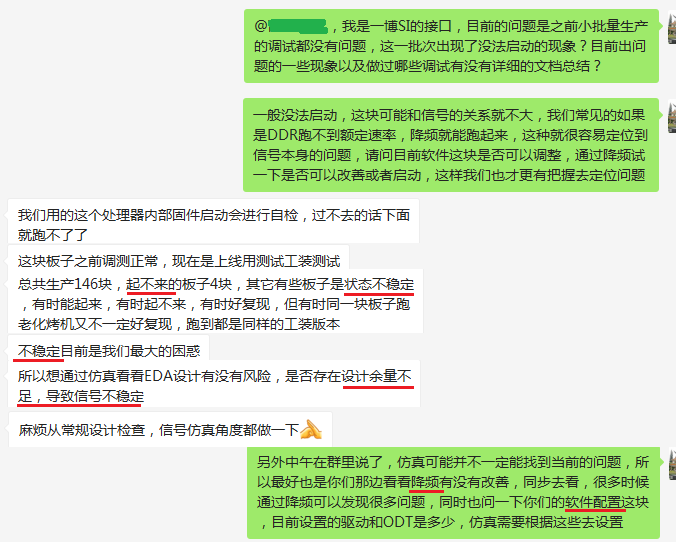

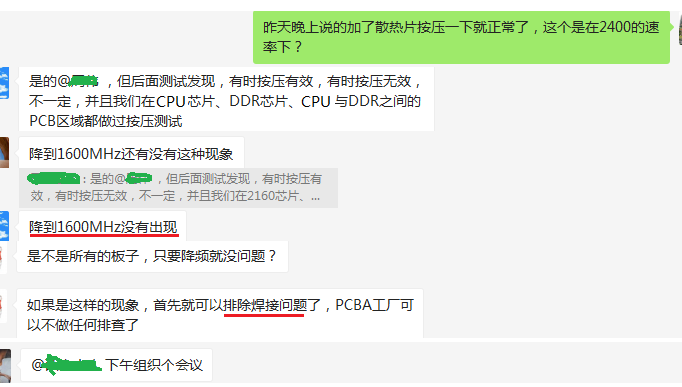

问题主要如下群聊内容所示:

初始反馈的信息可以总结一下就是:前面做了多次小批量一站式的试产,都没有出现过问题,本次在我司生产完测试没有问题,拉到客户端测试就有时好时坏的现象,主要问题是CPU在启动过程中DDR初始化失败,还没有找到解决方案,导致整机生产发货严重脱离计划节点,也就是整个项目的交期延迟了。

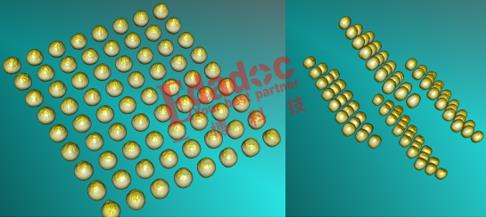

客户问题无小事,这是我们的服务宗旨。我们立即和客户一起成立了项目攻关组,大家分头行动,从自己的专业角度去提供各自的一些解决问题的方法。在焊接领域,客户提出了虚焊的可能,同时也说到重新焊接了CPU芯片的板子后面状态就正常了,所以首先安排一些启动异常的板子拿去焊接厂用3D X-ray看看是否有虚焊的可能,焊接厂反馈回来的部分结果如下所示。

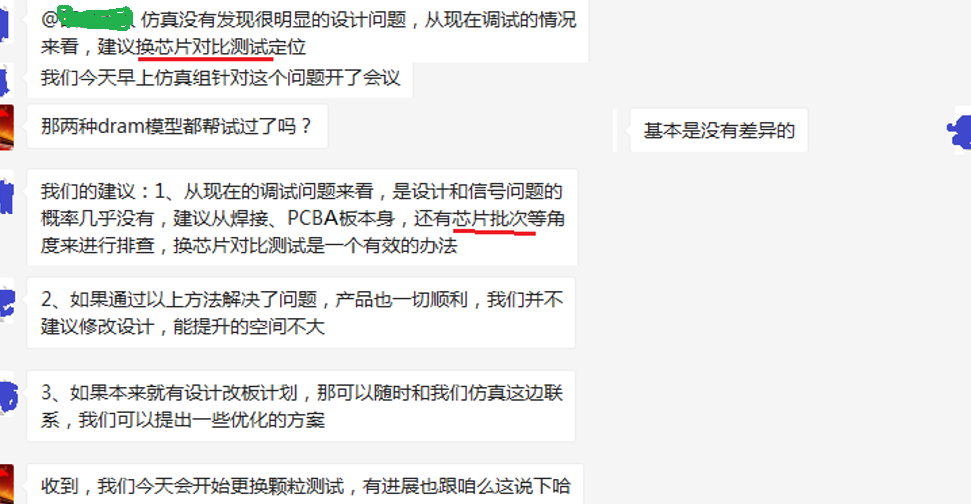

深圳和珠海工厂的3D x-ray检测结果出来了,都没有发现焊接问题,CT扫描非常耗时,深圳昨天寄过去的板子建议就不要照了,没有多大意义;附件为珠海工厂3D x-ray检测设备检测结果如附件,没有发现锡球不规则、无枕头效应、无大小锡球等问题。

术业有专攻,虽然看不懂3D X-ray的结果,但从图片来看,肉眼基本看不出太大的差别,作为门外汉的我看到的就是焊球基本一样,颗粒饱满均匀,没有出现某单个球有明显的不规则缺陷,可以初步排除这个板子虚焊的可能。这也是我们工厂的大利(sha)器,焊接质量好不好一照便知。虽然照了3D,但我们还是又对调了好板子上的芯片并重新进行了焊接测试,问题还是没有解决。

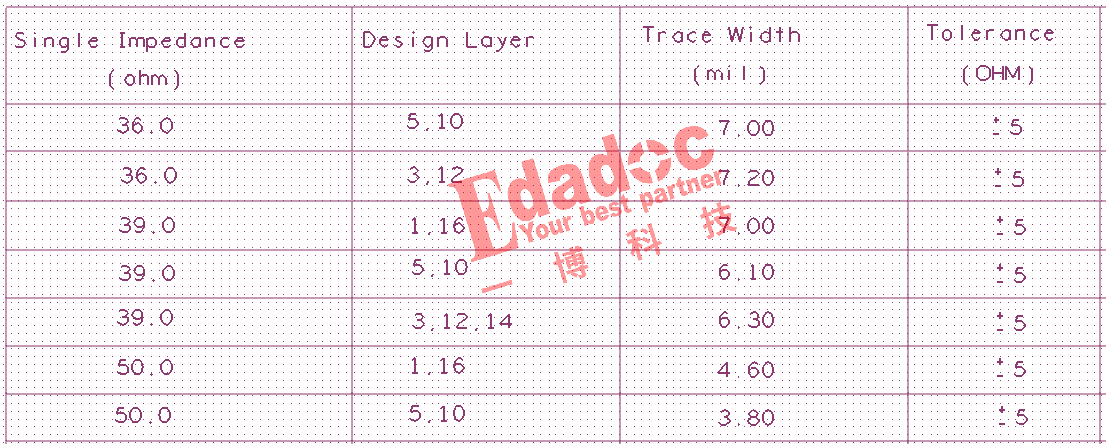

焊接排除的同时,我们也在同步对PCB制板进行排除验证,制板的检验,除了切片等破坏性测试外,和信号电气相关的就是看阻抗是否满足制板要求,这个可以通过实测线路阻抗来验证,于是该我们的67GHz网分上场了。板子到了我们的高速实验室,我们马上就进行了DDR4信号部分的阻抗测试,如下是DDR4单线部分设计的阻抗要求。

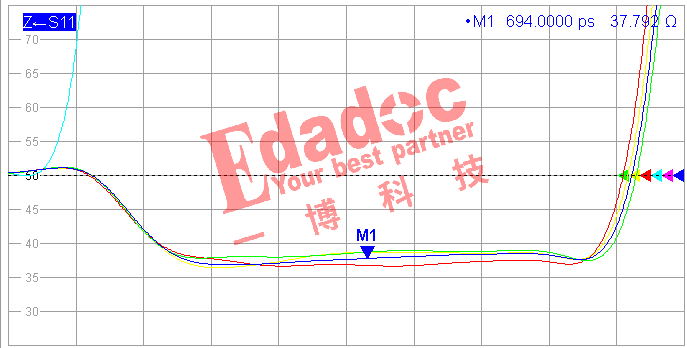

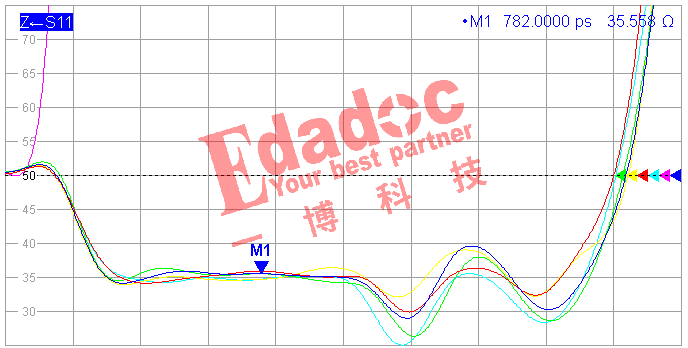

部分实际测试的阻抗如下图所示。

数据信号阻抗要求39±5ohm,实测阻抗在36~40ohm,阻抗满足要求。

地址控制信号阻抗要求36±5ohm,实测主干段线路阻抗在35.6ohm左右,阻抗满足要求。

从阻抗实测的结果来看,基本可以排除PCB制板的问题,所以这个时候从信号完整性的角度开始了我们常规性套路的排查。

首先就是了解一下问题发生的情况,看看哪些现象可能是信号完整性造成的,比如降频是否工作,一般DDRx降频能工作的,基本就可以排除焊接、硬件原理方面的问题,然后集中精力从PCB设计、电源噪声、信号质量及软件配置等方面看看是不是系统时序裕量不足造成的问题。

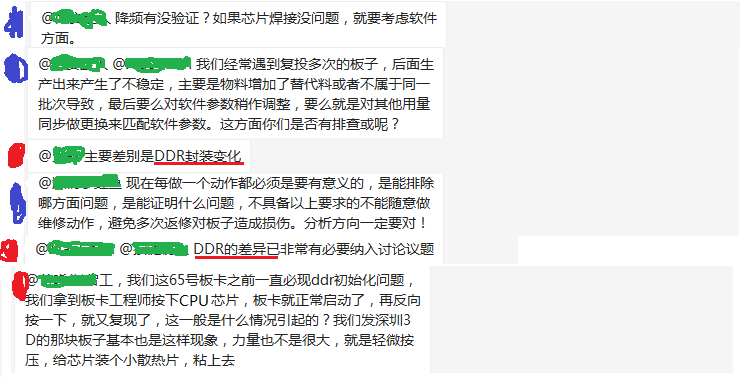

此时出来了两个小插曲,一个是客户反馈本次颗粒换了另一个型号的料号,封装上有一点小小的改动,但引脚什么的都没有变化,这是本次和上次硬件上唯一的区别;另一个就比较诡异了,客户反馈之前不行的,装个散热片按压下又好了,反向按压下又不好了(这个感觉有点像灵异事件,其实我们也经常听其他客户提到过),这导致我们定位问题变得又扑朔迷离了。

新的反馈导致我们有了新的方向和初步的结论,就是调换之前的颗粒重新焊接再测试下,如果问题解决那就万事大吉。

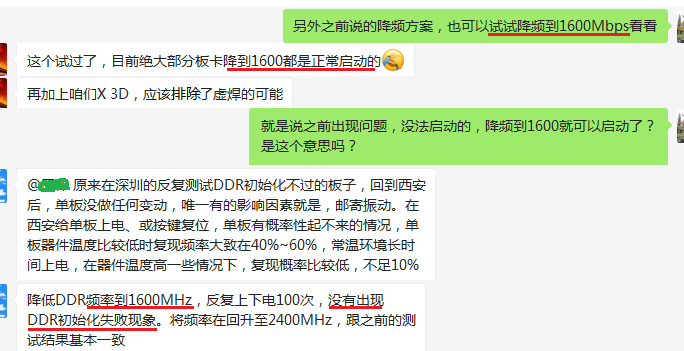

另一方面我们还想按照我们的常规套路降频再尝试(挣扎)一下,客户也非常的配合,但接下来的结论又把问题引到了一个新的方向。

降频的方案说明有效果,之前出问题的现象重复多次不再复现,这个就可以果断排除硬件原理、虚焊的可能,剩下的还是要从系统的时序裕量不足上去排除。另外之前吊诡的按压现象也只是偶然的成功现象,不足以作为解决问题的方向,所以只能算是查找问题过程中的一个小插曲,进一步排除了虚焊的可能,也进一步说明了我们套路上一开始的思路是对的,只是中间方向太多,客户也没闲着,比我们更着急,所以各项工作都是相互并行在走。

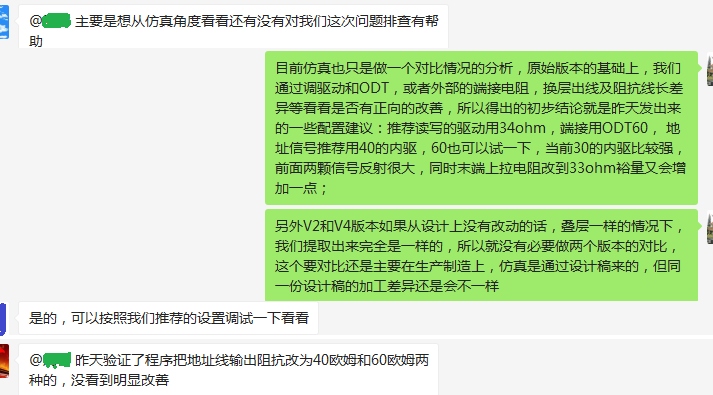

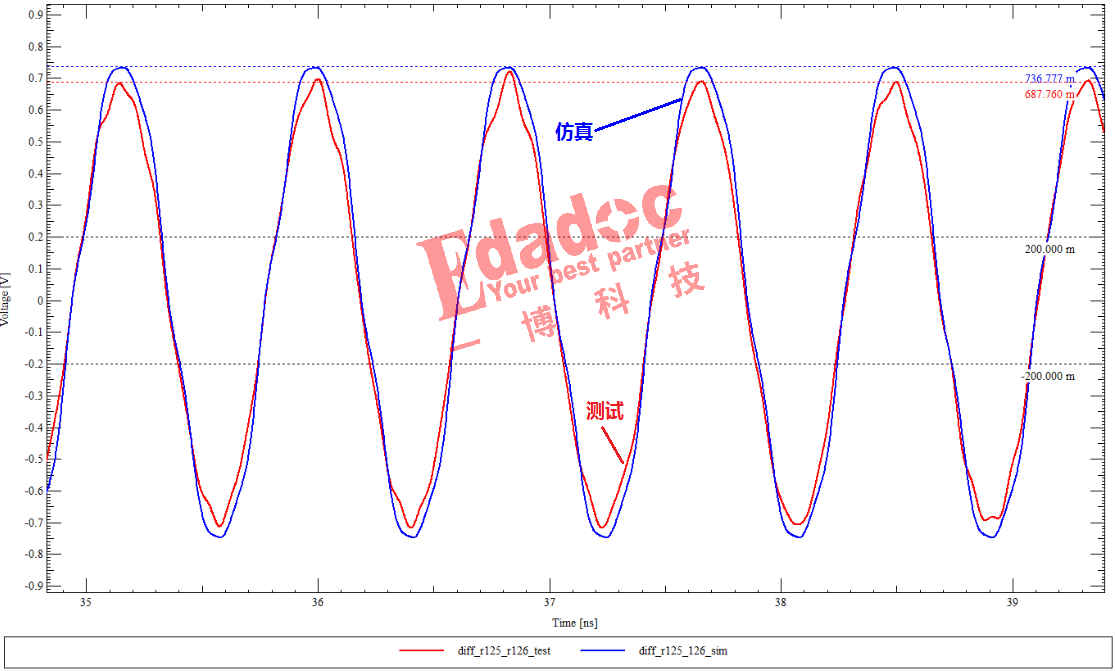

系统时序裕量不足,这个确实是可以通过仿真和实测对比的手段去定位,于是找到压死骆驼最后一根稻草的任务又落在了我们身上。

对于这种有实物的板子,我们的套路一般是先通过示波器测到板子上实际的信号,然后将实测的波形数据导入到仿真软件中和仿真结果进行对比,如果在同样的位置上仿真和测试波形一致,那么就基本可以确定芯片的模型是比较准确的,然后就可以通过仿真看到芯片内部真实的接收波形,从而根据波形好坏来定位问题。而目前的板子由于

DDR4

颗粒是正反贴片,除了焊接

DDR4 interposer

夹具我们没法通过常规的手段来测试,但时间宝贵,最后我们退而求其次,在时钟信号的端接电阻处进行了测试,一般时钟信号不需要任何其他的命令,只要系统可以跑起来就一直会有波形,所以我们可以先在时钟的端接电阻上测试到信号,然后在同样的位置上进行仿真对比,仿真和实测的部分对比结果如下图所示。

信号波形本身的质量还不错,从波形来看,两者上升沿和下降沿基本可以完全对齐,除了幅度上有一些小的差异外,其他基本都是可以对上的,所以这个也可以反映出芯片的模型是可信的,仿真的结果可信,可以进行下一步全面的信号及时序仿真排除了。

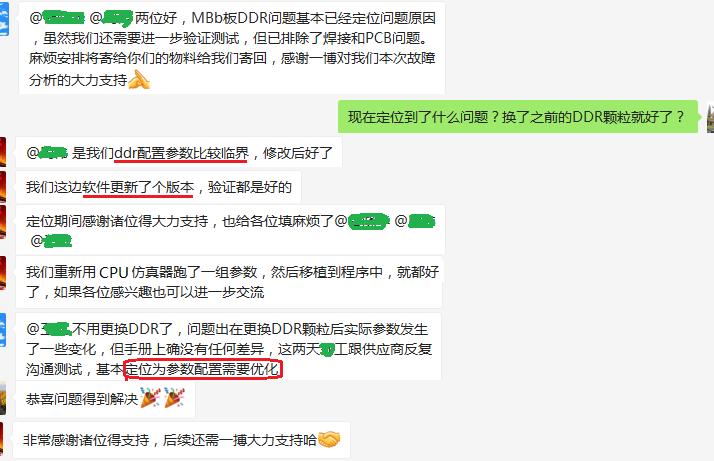

就在我们准备大展拳脚开始仿真的时候,客户突然说问题找到了,原来还真是软件配置的问题,由于更换DDR4颗粒后实际参数发生了变化,而配置软件还是按照之前的参数在控制,导致系统参数比较临界,产生了部分系统不稳定现象,最终更新了软件的配置参数,问题得到解决。

问题兜兜转转,没想到竟然以这种意想不到的结果结束,真是幸福来得太快就像龙卷风,我竟有点措手不及的感觉,我们的工程师豹哥就是被太多这种摸不着头脑的“幸福”搞秃的。

所幸问题最终定位了,豹哥也松了口气,虽然一波三折没有直接定位到问题,但大家积极配合的态度还是充分得到了客户的认可。从这个案例里面豹哥也得出了一些调试的套路,总结如下也和各位吃瓜粉丝们一起分享:

1、对于大多数信号问题,可以先降频试试,如果降到了最低还是没有任何改善,通常就需要从其他方面如硬件原理、软件、制板或焊接等去找问题了,如果降频有改善,那就和信号本身有关,可以从信号质量、电源、时序及软件配置等方面去找问题;

2、工欲善其事,必先利其器。在本次查找问题过程中,我们先后动用了3D X-ray、CT扫描(扫描比较慢,文章没有秀出来)、BGA返修台、67GHz ZVA矢量网络分析仪、59GHz示波器、仿真工具等,这好比对待一个重症患者,各种仪器齐上阵,最终通过先进的仪器来查出病症,对症下药。要想在PCB这个行业有所突破,没有这几把刷子也只能是徒劳。记得有位前辈戏谑过,以前在调试前都是要先去旁边的庙里拜一拜,也间接说明调试确实不是那么容易的事,只能说坑(套路)太多。

大家在调试过程中遇到过哪些坑,也一起来分享下吧。