明明设计的是高带宽,差点加工成开路?

发布时间:2022-06-27 15:29

作者:一博科技高速先生成员 黄刚

有没有感觉最近只看到了东哥的文章,是不是一度以为我们**了呢。没有啦,在这里还是要郑重的和广大的粉丝们解释下,高速先生这段时间一直在积累一些很有趣的素材,学习一些新的技术,以便给大家看到更多富有启发性的文章,这不我们又来了吗!

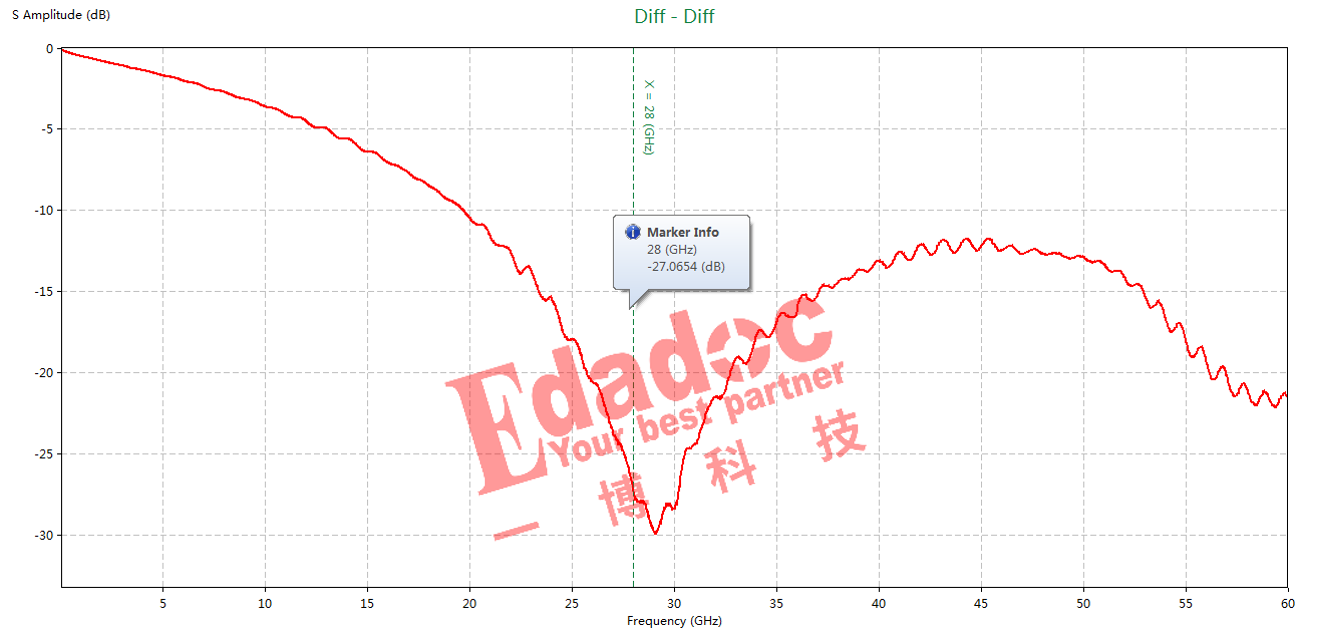

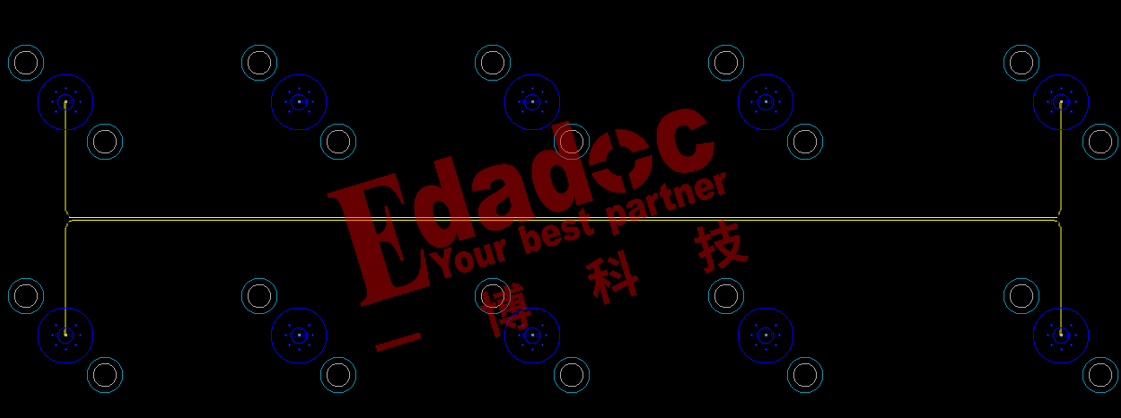

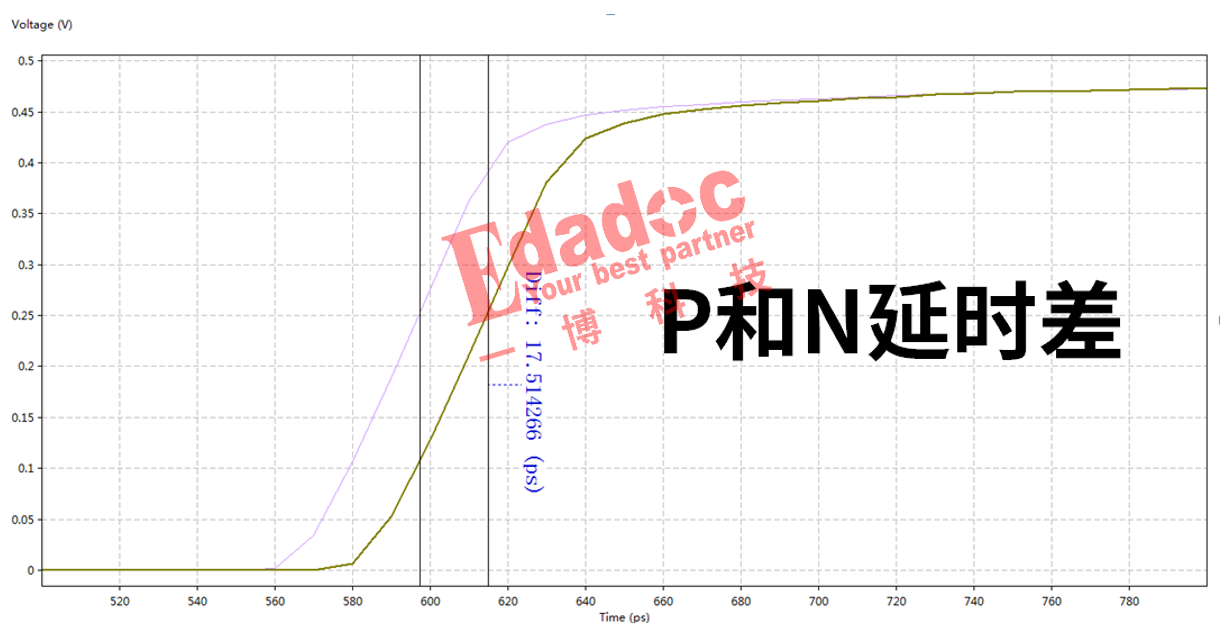

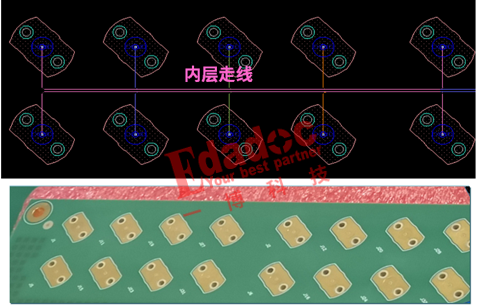

当我们测试到一对带1.85同轴连接器的内层走线时,测出了让我们意想不到的结果。设计就是一对差分线,我们主要是看看一款高速板材的损耗和加上同轴连接器后,链路的带宽和线性度能去到多高频率。

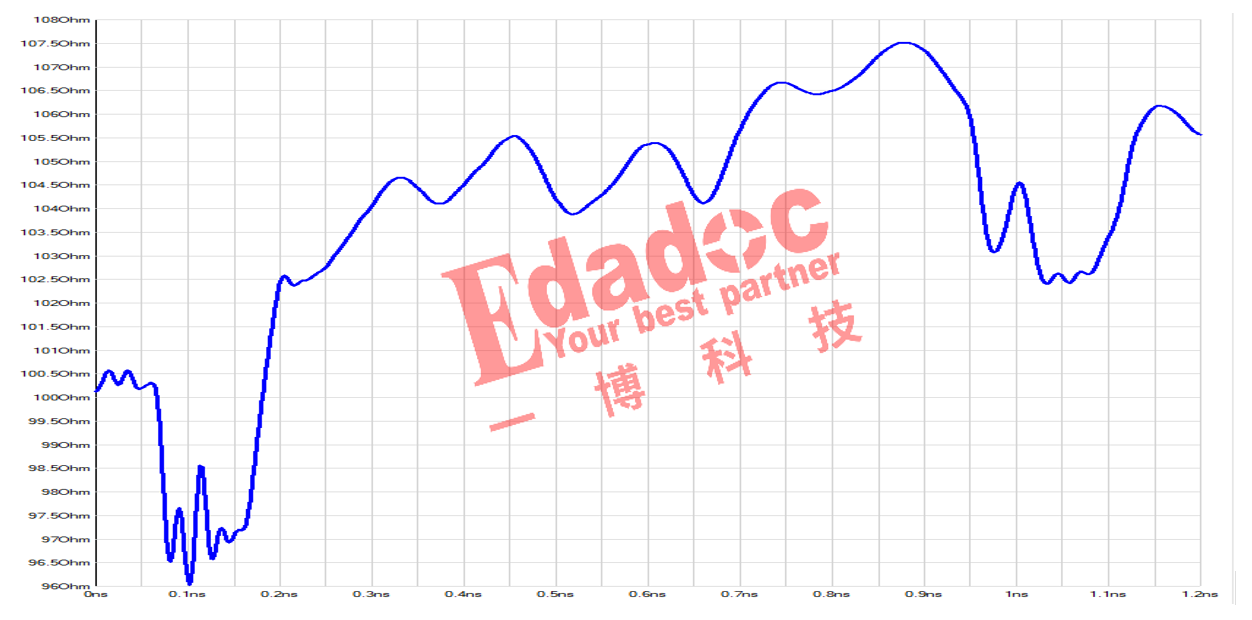

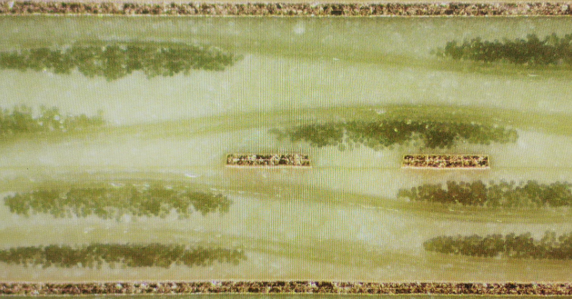

我们首先关注下同轴连接器位置的阻抗和差分线的阻抗,第一反应,感觉还是不错的,尤其是走线,整个链路的阻抗都在±5%以内,虽然不能算特别优秀,但是心理至少能接受的那种。

有没有感觉最近只看到了东哥的文章,是不是一度以为我们**了呢。没有啦,在这里还是要郑重的和广大的粉丝们解释下,高速先生这段时间一直在积累一些很有趣的素材,学习一些新的技术,以便给大家看到更多富有启发性的文章,这不我们又来了吗!

当我们测试到一对带1.85同轴连接器的内层走线时,测出了让我们意想不到的结果。设计就是一对差分线,我们主要是看看一款高速板材的损耗和加上同轴连接器后,链路的带宽和线性度能去到多高频率。

我们首先关注下同轴连接器位置的阻抗和差分线的阻抗,第一反应,感觉还是不错的,尤其是走线,整个链路的阻抗都在±5%以内,虽然不能算特别优秀,但是心理至少能接受的那种。